UNIDENTIFIED

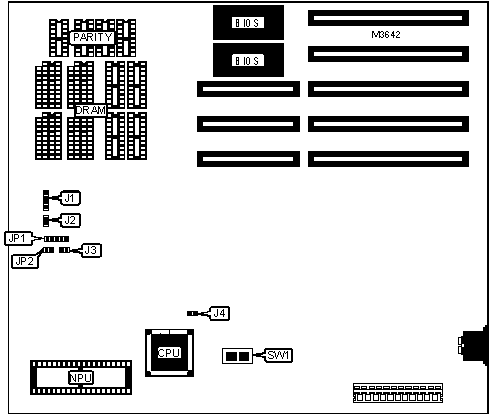

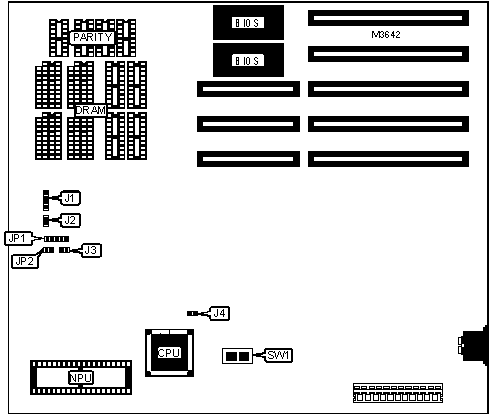

PETER-286 (VER. 2.00)

|

Processor |

80286 |

|

Processor Speed |

12MHz |

|

Chip Set |

G-2 |

|

Video Chip Set |

None |

|

Maximum Onboard Memory |

1MB |

|

Maximum Video Memory |

None |

|

Cache |

None |

|

BIOS |

AMI/Award |

|

Dimensions |

218mm x 218mm |

|

I/O Options |

None |

|

NPU Options |

80287 |

|

CONNECTIONS | |||

|

Purpose |

Location |

Purpose |

Location |

|

Speaker |

J1 |

Power LED & keylock |

JP1 |

|

Reset switch |

J2 |

Turbo switch |

JP2 |

|

Turbo LED |

J3 | ||

|

USER CONFIGURABLE SETTINGS | |||

|

Function |

Label |

Position | |

|

Parity enabled |

J4 |

Closed | |

|

Parity disabled |

J4 |

Open | |

|

Monitor type select color |

SW1/1 |

On | |

|

Monitor type select monochrome |

SW1/1 |

Off | |

|

0 wait state enabled |

SW1/2 |

On | |

|

0 wait state disabled |

SW1/2 |

Off | |

|

DRAM CONFIGURATION | ||||

|

Size |

Bank 0 |

P 0 |

Bank 1 |

P 1 |

|

512KB |

(4) 44256 |

(2) 41256 |

None |

None |

|

640KB |

(4) 44256 |

(2) 41256 |

(4) 4464 |

(2) 4164 |

|

1MB |

(4) 44256 |

(2) 41256 |

(4) 44256 |

(2) 41256 |

|

Note: The location of banks 0 & 1, and P 0 & P 1 are unidentified. | ||||

|

DRAM SWITCH CONFIGURATION | ||

|

Size |

SW1/3 |

SW1/4 |

|

512KB |

On |

Off |

|

640KB |

Off |

On |

|

1MB |

Off |

Off |